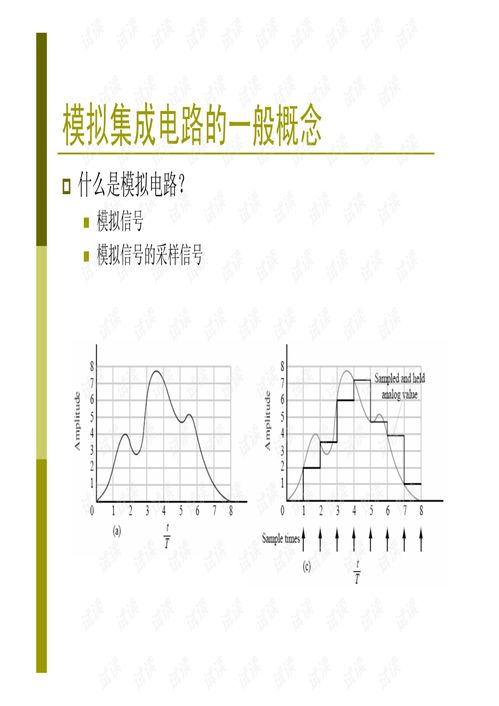

在當今數字技術主導的時代,模擬CMOS集成電路(Analog CMOS IC)設計依然扮演著無可替代的角色,它是連接真實模擬世界與數字處理系統的關鍵橋梁。本PPT旨在提煉模擬CMOS設計的核心精髓,為初學者與工程師提供一個清晰、系統的知識框架。

一、 設計哲學與基礎

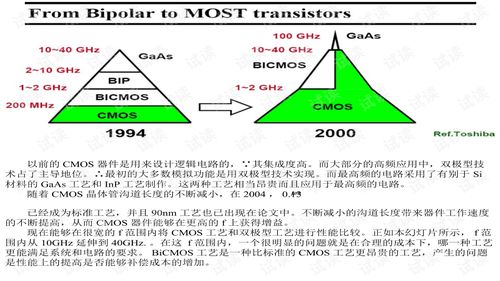

模擬設計的核心是處理連續變化的電壓與電流信號,其目標是在功耗、面積、速度、精度和魯棒性之間取得最佳平衡。CMOS工藝因其低功耗、高集成度和優秀的縮放特性,成為現代模擬IC的主流技術。設計者必須深刻理解MOS晶體管的工作區域(截止區、線性區、飽和區)及其小信號模型,這是所有復雜電路構建的基石。

二、 核心模塊設計精要

- 單級放大器:共源、共柵、共漏(源極跟隨器)及其組合是基本構建塊。關鍵在于理解增益、帶寬、輸入/輸出阻抗和擺幅之間的折衷。

- 差分對與電流鏡:差分結構是抑制共模噪聲、提高電源抑制比(PSRR)的核心。電流鏡則提供穩定的偏置與有源負載,其匹配性直接決定電路精度。

- 運算放大器:作為“模擬電路的工作馬”,其設計是模擬技術的集大成者。需重點關注開環增益、單位增益帶寬、相位裕度(穩定性)、壓擺率和噪聲性能。兩級運放與頻率補償技術是經典課題。

- 基準電壓源:如帶隙基準,利用硅的物理特性產生與電源和溫度無關的穩定電壓,是系統精度的保障。

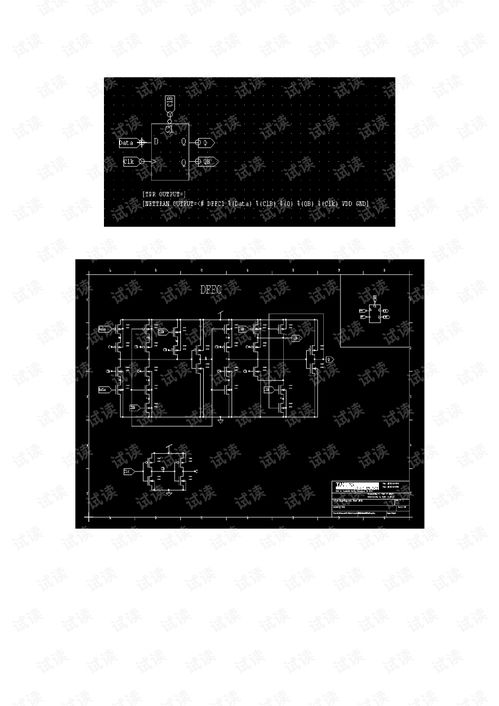

三、 設計流程與仿真驗證

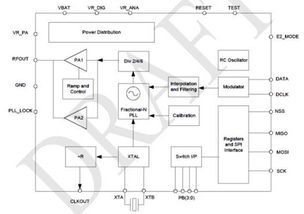

一個穩健的設計遵循系統化流程:指標定義 → 架構選擇 → 電路設計與手工計算 → 原理圖仿真(DC、AC、瞬態、噪聲等) → 版圖設計與物理驗證(DRC、LVS) → 后仿真。其中,版圖階段對模擬性能影響巨大,必須考慮匹配、寄生、噪聲耦合和襯底干擾等問題。

四、 先進議題與挑戰

隨著工藝節點不斷演進,低壓設計、短溝道效應(如速度飽和)、器件失配加劇以及1/f噪聲等問題日益突出。設計者需掌握共源共柵、增益提升、開關電容電路等先進技術來應對挑戰。混合信號集成中的襯底噪聲隔離和電源完整性管理也變得至關重要。

五、

模擬CMOS設計是一門結合了深刻物理洞察、嚴謹數學分析和精湛工程技藝的藝術。它沒有唯一的“正確答案”,而是在多重約束下的最優解探索。精通這門藝術,意味著不僅能讀懂電路,更能預見并駕馭工藝變化、溫度漂移和噪聲帶來的不確定性,最終在硅片上實現可靠而優雅的信號處理功能。

(本PPT內容可作為學習與研討的綱領,建議結合經典教材《模擬CMOS集成電路設計》及實際項目進行深入實踐。)