專用集成電路(Application-Specific Integrated Circuit,簡稱ASIC)是指為特定應(yīng)用或特定用戶需求而專門設(shè)計、制造的集成電路。與通用集成電路(如CPU、GPU等)相比,ASIC在性能、功耗、面積和成本方面往往具有顯著優(yōu)勢,因此在現(xiàn)代電子系統(tǒng)中扮演著至關(guān)重要的角色。

一、ASIC設(shè)計的基本流程

ASIC設(shè)計是一個復(fù)雜而系統(tǒng)化的工程過程,通常包括以下幾個主要階段:

- 需求分析與規(guī)格制定:明確芯片的功能、性能、功耗、接口等要求。

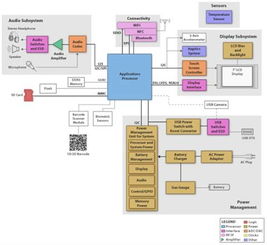

- 架構(gòu)設(shè)計:確定芯片的整體結(jié)構(gòu),包括模塊劃分、總線設(shè)計、時鐘和電源規(guī)劃等。

- 邏輯設(shè)計與驗證:使用硬件描述語言(如Verilog或VHDL)進行寄存器傳輸級(RTL)設(shè)計,并通過仿真驗證其功能正確性。

- 綜合與優(yōu)化:將RTL代碼轉(zhuǎn)換為門級網(wǎng)表,并進行時序、面積和功耗優(yōu)化。

- 物理設(shè)計:包括布局規(guī)劃、布線、時鐘樹綜合、電源規(guī)劃等,生成可用于制造的版圖。

- 驗證與測試:進行版圖后仿真、形式驗證以及制定測試方案,確保芯片可制造且功能可靠。

- 流片與封裝:將設(shè)計交付給晶圓廠進行制造,完成后進行封裝和測試。

二、ASIC的關(guān)鍵技術(shù)

- 低功耗設(shè)計:隨著移動設(shè)備和物聯(lián)網(wǎng)的普及,功耗成為關(guān)鍵指標。技術(shù)包括時鐘門控、電源門控、多電壓域設(shè)計等。

- 高性能設(shè)計:通過流水線、并行處理、專用硬件加速等方法提升處理速度。

- 可測性設(shè)計(DFT):插入掃描鏈、內(nèi)建自測試(BIST)等結(jié)構(gòu),以提高芯片的可測試性和良率。

- 可靠性設(shè)計:考慮抗噪聲、熱管理、老化效應(yīng)等因素,確保芯片在惡劣環(huán)境下穩(wěn)定工作。

三、ASIC的應(yīng)用領(lǐng)域

ASIC已廣泛應(yīng)用于各個行業(yè):

- 消費電子:智能手機中的基帶芯片、圖像處理芯片等。

- 通信設(shè)備:路由器、交換機的網(wǎng)絡(luò)處理芯片。

- 汽車電子:自動駕駛中的傳感器處理芯片、控制系統(tǒng)芯片。

- 人工智能:專用于神經(jīng)網(wǎng)絡(luò)計算的AI加速芯片。

- 工業(yè)控制:電機驅(qū)動、電源管理芯片等。

四、ASIC面臨的挑戰(zhàn)與發(fā)展趨勢

- 挑戰(zhàn):設(shè)計成本高昂、周期長;工藝節(jié)點演進帶來的物理效應(yīng)復(fù)雜化;人才短缺等。

- 發(fā)展趨勢:

- 異構(gòu)集成:將不同工藝、功能的芯片通過先進封裝技術(shù)集成在一起。

- 敏捷設(shè)計:利用高層次綜合(HLS)、基于平臺的設(shè)計方法縮短開發(fā)周期。

- 開源生態(tài):RISC-V等開源指令集架構(gòu)降低設(shè)計門檻,促進創(chuàng)新。

專用集成電路設(shè)計是電子信息技術(shù)的基礎(chǔ)與核心。隨著5G、人工智能、物聯(lián)網(wǎng)等新興技術(shù)的快速發(fā)展,ASIC將繼續(xù)朝著高性能、低功耗、高集成度的方向演進,并在更多領(lǐng)域發(fā)揮不可替代的作用。掌握ASIC設(shè)計與應(yīng)用的知識,對于投身于半導(dǎo)體行業(yè)的工程師而言,是至關(guān)重要的技能與素養(yǎng)。