隨著高壓集成電路在功率管理、汽車電子、工業(yè)控制及顯示驅(qū)動等領(lǐng)域的廣泛應(yīng)用,對能夠在惡劣高壓環(huán)境下穩(wěn)定工作的基準(zhǔn)電壓源的需求日益迫切。基準(zhǔn)電壓源作為模擬與混合信號集成電路的核心模塊之一,其性能直接決定著整個系統(tǒng)的精度、穩(wěn)定性和可靠性。本文探討一種專為高壓集成電路設(shè)計的基準(zhǔn)電壓源方案,旨在實(shí)現(xiàn)高精度、低溫漂、高電源抑制比及寬輸入電壓范圍等關(guān)鍵特性。

一、 高壓基準(zhǔn)源的設(shè)計挑戰(zhàn)

在高壓(如數(shù)十伏至數(shù)百伏)工作條件下,設(shè)計基準(zhǔn)電壓源面臨諸多獨(dú)特挑戰(zhàn)。常規(guī)的低壓CMOS或Bipolar工藝器件無法承受如此高的電壓,必須采用特殊的高壓器件或電路結(jié)構(gòu),如LDMOS、垂直雙擴(kuò)散MOSFET或級聯(lián)拓?fù)洹8邏合碌墓目刂啤嵝?yīng)以及長期可靠性問題更為突出。高壓電源通常存在較大的紋波和噪聲,要求基準(zhǔn)源具備極高的電源抑制比以維持輸出純凈。溫度變化對器件參數(shù)的影響在高電壓下可能被放大,導(dǎo)致基準(zhǔn)電壓的溫度系數(shù)惡化。

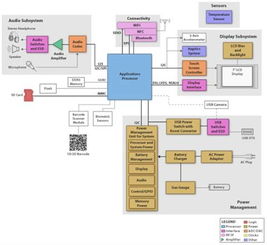

二、 電路架構(gòu)選擇與核心原理

針對上述挑戰(zhàn),本文提出的設(shè)計采用帶隙基準(zhǔn)原理與高壓自偏置技術(shù)相結(jié)合的核心架構(gòu)。帶隙基準(zhǔn)因其能夠利用硅材料的帶隙電壓這一與工藝、溫度相關(guān)性弱的物理常數(shù),是實(shí)現(xiàn)低溫度系數(shù)的理想選擇。

- 高壓啟動與偏置電路:設(shè)計一個獨(dú)立的高壓啟動電路,確保在電源上電瞬間,核心偏置點(diǎn)能夠迅速脫離零電流狀態(tài),進(jìn)入正常工作區(qū)。由核心基準(zhǔn)電路自身產(chǎn)生的穩(wěn)定偏置電壓通過反饋回路維持正常工作,實(shí)現(xiàn)自偏置,降低對啟動電路的依賴和靜態(tài)功耗。

- 帶隙核心與曲率補(bǔ)償:核心采用一階帶隙基準(zhǔn)結(jié)構(gòu),通過將兩個具有不同電流密度或類型的雙極型晶體管(可利用高壓工藝中的寄生BJT或?qū)iT設(shè)計)的正向結(jié)電壓之差進(jìn)行比例放大,并與其中一個結(jié)電壓相加,產(chǎn)生近似零溫度系數(shù)的基準(zhǔn)電壓。為進(jìn)一步優(yōu)化溫度特性,引入了高階曲率補(bǔ)償技術(shù),例如利用MOSFET的亞閾值特性或額外的溫度傳感電路,補(bǔ)償高階非線性項(xiàng),使溫度系數(shù)在更寬的溫度范圍(如-40°C至150°C)內(nèi)保持極低水平。

- 高壓調(diào)節(jié)與輸出級:核心產(chǎn)生的低壓帶隙基準(zhǔn)(約1.2V)通過一個高精度、高輸入阻抗的運(yùn)算放大器緩沖。該運(yùn)放采用高壓器件設(shè)計,其電源軌直接來自高壓輸入。運(yùn)放的輸出驅(qū)動一個由高壓MOSFET構(gòu)成的調(diào)整管,構(gòu)成一個電壓跟隨器或低壓差線性穩(wěn)壓器結(jié)構(gòu),最終輸出一個不受負(fù)載變化影響的穩(wěn)定高壓基準(zhǔn)電壓(例如5V或10V)。此結(jié)構(gòu)能有效隔離高壓輸入噪聲,并提供良好的負(fù)載調(diào)整率。

- 電源抑制增強(qiáng)技術(shù):為提高電源抑制比,在核心電流鏡和運(yùn)放設(shè)計中采用共源共柵結(jié)構(gòu),顯著提升輸出阻抗。在電源入口處可集成片上去耦電容或采用預(yù)穩(wěn)壓技術(shù),對提供給核心電路的電源進(jìn)行初步濾波和穩(wěn)定。

三、 關(guān)鍵性能指標(biāo)與仿真驗(yàn)證

該設(shè)計的預(yù)期關(guān)鍵性能指標(biāo)包括:

- 輸入電壓范圍:12V 至 60V(可依據(jù)工藝擴(kuò)展)。

- 輸出電壓:5.0 V ± 1%。

- 溫度系數(shù):< 20 ppm/°C (-40°C ~ 125°C)。

- 電源抑制比:> 80 dB @ 100 Hz, > 60 dB @ 1 kHz。

- 線性調(diào)整率:< 0.1%/V。

- 負(fù)載調(diào)整率:< 0.1% (負(fù)載電流 0-10mA)。

采用先進(jìn)的高壓BCD工藝進(jìn)行電路設(shè)計與仿真驗(yàn)證。仿真內(nèi)容涵蓋直流工作點(diǎn)分析、溫度掃描分析、交流小信號分析(用于PSRR和穩(wěn)定性評估)以及瞬態(tài)分析(包括上電啟動過程和負(fù)載瞬態(tài)響應(yīng))。仿真結(jié)果需確認(rèn)電路在所有工藝角、溫度范圍和輸入電壓范圍內(nèi)均能穩(wěn)定啟動并輸出符合規(guī)格的基準(zhǔn)電壓,同時保證足夠的相位裕度以避免振蕩。

四、 版圖設(shè)計與可靠性考慮

高壓基準(zhǔn)源的版圖設(shè)計至關(guān)重要。必須嚴(yán)格遵守工藝設(shè)計規(guī)則中關(guān)于高壓器件間距、場氧保護(hù)環(huán)、隔離等要求,以防止閂鎖效應(yīng)和高壓擊穿。核心的低壓敏感部分(如帶隙核心和運(yùn)放輸入對)應(yīng)采用保護(hù)環(huán)與高壓部分進(jìn)行物理隔離,并盡可能遠(yuǎn)離高壓器件以減小噪聲耦合和熱梯度影響。電源和地線應(yīng)設(shè)計為寬金屬線以降低寄生電阻和電感。對于功率耗散較大的高壓調(diào)整管,需考慮足夠的散熱面積和金屬布線。

五、 結(jié)論

本文闡述了一種適用于高壓集成電路的基準(zhǔn)電壓源設(shè)計方案。該方案通過融合成熟的帶隙基準(zhǔn)原理與針對高壓環(huán)境優(yōu)化的電路技術(shù),包括高壓自偏置啟動、曲率補(bǔ)償、高壓輸出緩沖及增強(qiáng)的電源抑制措施,有效應(yīng)對了高壓應(yīng)用帶來的特殊挑戰(zhàn)。通過合理的架構(gòu)選擇和嚴(yán)謹(jǐn)?shù)姆抡媾c版圖設(shè)計,該基準(zhǔn)源有望實(shí)現(xiàn)高精度、高穩(wěn)定性和高可靠性,為各類高壓模擬及混合信號IC提供穩(wěn)定的電壓參考,滿足汽車、工業(yè)等嚴(yán)苛應(yīng)用場景的需求。未來的工作可聚焦于進(jìn)一步降低功耗、擴(kuò)展輸入電壓范圍以及集成更先進(jìn)的數(shù)字修調(diào)技術(shù)以實(shí)現(xiàn)出廠前的高精度微調(diào)。