在掌握了反相器原理圖設計與前仿真的基礎上,本篇筆記將重點介紹集成電路物理實現的關鍵一步:版圖設計與后仿真。

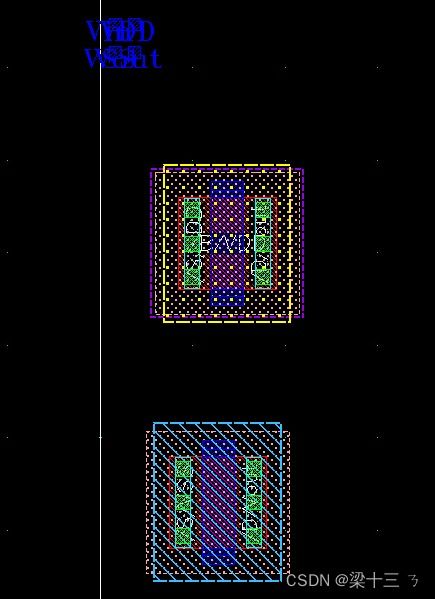

一、 反相器版圖設計

版圖是連接電路設計與芯片制造的橋梁,它將抽象的電路符號轉換為制造光刻掩模所需的精確幾何圖形。

- 準備工作:

- 啟動Virtuoso Layout Editor,調用已完成的CMOS反相器原理圖單元。

- 設置正確的工藝設計套件技術文件,確保圖層、設計規則與目標工藝完全匹配。

- 核心器件繪制:

- PMOS管:在N阱中繪制,需包含有源區、多晶硅柵、P+注入、接觸孔及金屬連線。柵極需與NMOS柵極相連,構成輸入端。

- NMOS管:在P襯底(或P阱)中繪制,包含有源區、多晶硅柵、N+注入、接觸孔及金屬連線。

- 注意PMOS與NMOS的尺寸需嚴格匹配原理圖中的寬長比。

- 連接與布線:

- 輸出端:將PMOS的漏極與NMOS的漏極用金屬線(如Metal1)連接,此連接點即為反相器的輸出端。

- 電源與地:PMOS的源極連接至VDD電源線(通常用高層金屬);NMOS的源極連接至VSS地線。

- 輸入端:將兩管的柵極用多晶硅或金屬連接,構成輸入端。

- 設計規則檢查:

- 完成繪制后,必須運行DRC,檢查版圖是否符合工藝廠的所有最小間距、寬度、覆蓋等物理規則。這是保證芯片可制造性的底線。

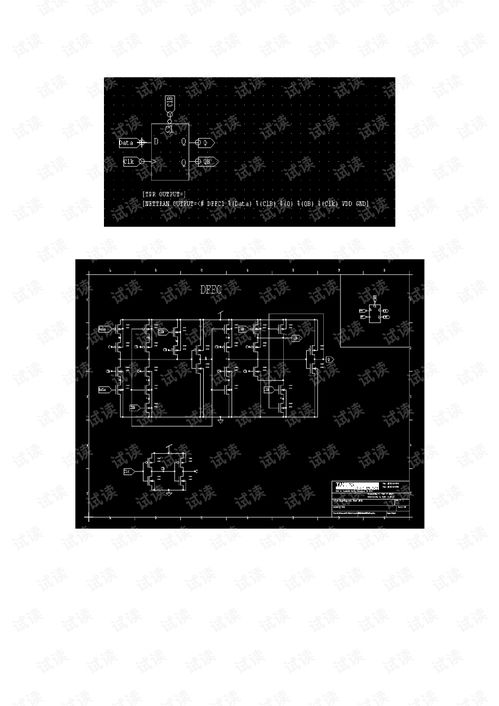

- 版圖與原理圖一致性檢查:

- 運行LVS,將提取出的版圖網表與原始原理圖網表進行比對,確保兩者在電氣連接上完全一致,無短路、開路或器件匹配錯誤。

二、 寄生參數提取與后仿真

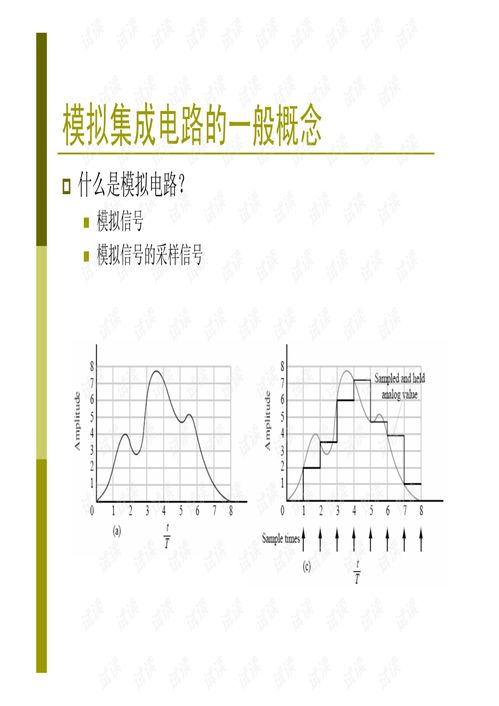

版圖完成后,電路性能會受實際布線引入的寄生電阻、電容影響,必須通過后仿真進行驗證。

- 寄生參數提取:

- 在通過DRC和LVS后,使用工具提取版圖的寄生參數(PEX)。

- 提取模式通常選擇“R+C”或“R+C+CC”,以獲取寄生電阻、對地電容以及線間耦合電容。

- 后仿真設置:

- 生成一個包含所有寄生元件的“后提取”網表或視圖。

- 在ADE仿真環境中,將待仿真的電路視圖切換為此帶寄生的視圖。

- 關鍵性能對比分析:

- 瞬態特性:施加與“前仿真”相同的輸入方波,觀察輸出波形。重點關注:

- 延時:通常由于寄生電容充電,上升/下降時間及傳輸延時會增加。

- 波形完整性:檢查是否存在因寄生效應導致的過沖、回溝或振蕩。

- 直流特性:再次仿真電壓傳輸特性曲線,觀察邏輯閾值、噪聲容限是否有顯著偏移。

- 動態功耗:由于對寄生電容充放電,動態功耗通常會高于前仿真結果。

- 迭代優化:

- 若后仿真結果不滿足性能指標(如延時過大),需返回修改版圖。常見優化手段包括:加寬關鍵信號線以減少電阻,增大驅動管尺寸以加快對寄生電容的充放電,或優化布線以減少耦合電容。

- 修改后必須重新進行DRC、LVS和提取,形成“設計-驗證-優化”的閉環。

三、 與心得

從原理圖到版圖,是從理想世界走向物理現實的過程。反相器雖小,但其版圖設計與后仿真流程完整地體現了集成電路物理設計的核心:

- 嚴謹性:DRC/LVS的通過是后續一切工作的基礎,必須確保萬無一失。

- 折衷藝術:版圖設計是性能、面積、可靠性的多維折衷。例如,為了速度而增大晶體管或加寬金屬線,必然會犧牲面積。

- 寄生意識:優秀的模擬設計者必須具備“寄生意識”,在版圖階段就預見到關鍵節點的寄生影響,并通過合理的布局布線(如對稱性、屏蔽、匹配等)將其最小化。

至此,一個完整的反相器設計流程(原理圖、前仿真、版圖、后仿真)已走通。這為后續學習更復雜的電路模塊,如差分對、運放、比較器等,奠定了堅實的實踐基礎。下一步,可以嘗試設計一個帶負載電容的環形振蕩器,來綜合應用和驗證所學知識。