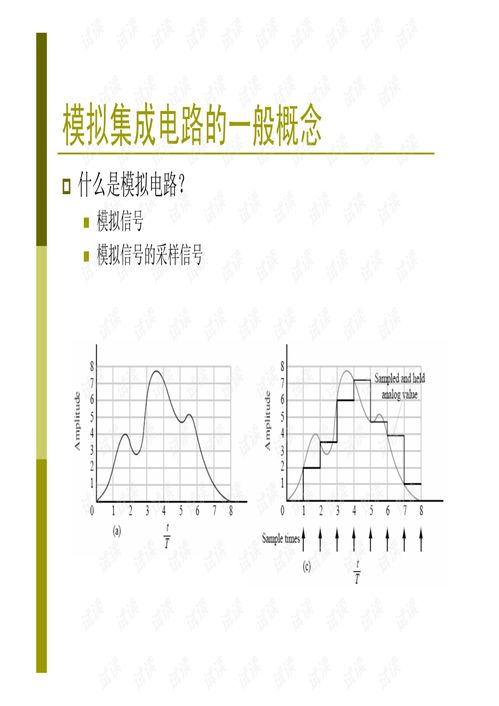

模擬BiCMOS(雙極互補金屬氧化物半導體)設計是集成電路領域一個關鍵且富有挑戰性的分支,它巧妙結合了雙極型晶體管(BJT)的高速度、高驅動能力和CMOS技術的低功耗、高集成度優勢。對于從事高性能模擬、射頻(RF)或混合信號芯片設計的工程師和學生而言,掌握其核心原理與設計流程至關重要。本文將探討如何利用CSDN等平臺的專業資源進行學習,并梳理集成電路設計中的關鍵考量。

一、模擬BiCMOS技術概述與設計挑戰

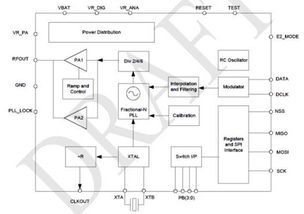

BiCMOS工藝允許在同一芯片上集成BJT和CMOS器件,使其非常適用于需要高速模擬前端(如放大器、比較器)與高密度數字邏輯或低功耗模塊共存的場景,例如高速數據轉換器、射頻收發機、汽車電子及精密傳感器接口。設計挑戰也隨之而來:工藝復雜度高導致成本增加;需要精心處理BJT與CMOS器件之間的匹配、隔離以及熱效應;設計時必須綜合考慮兩種器件截然不同的特性(如BJT的跨導、CMOS的輸入阻抗)以實現最優電路性能。

二、CSDN等平臺的專業資源價值與獲取指南

CSDN(中國開發者網絡)作為國內知名的IT技術社區,匯集了大量工程師分享的實踐經驗、學習筆記、設計文檔乃至工具腳本。對于模擬BiCMOS設計學習者,可以按以下方式高效利用:

- 精準搜索:使用關鍵詞組合進行搜索,例如“模擬BiCMOS設計流程”、“BiCMOS工藝庫使用”、“BJT與CMOS協同仿真”等。往往可以找到用戶上傳的PPT、PDF教程、項目或仿真代碼。

- 甄別質量:優先選擇點贊、收藏數高,且發布者具有相關行業背景認證的文檔。關注那些系統闡述從器件物理、工藝入門到具體電路(如BiCMOS運算放大器、Bandgap電壓基準源)設計的系列文章或資源。

- 實踐結合:許多資源會涉及具體EDA工具(如Cadence Virtuoso, Synopsys HSpice)的操作指南。下載后,應結合官方手冊和實際軟件環境進行動手練習,完成從原理圖輸入、仿真到版圖設計的全流程。

- 拓展渠道:除了CSDN,也應關注IEEE Xplore、arXiv等學術數據庫獲取前沿論文,以及廠商(如TSMC, GlobalFoundries)發布的工藝設計套件(PDK)文檔和設計手冊。

三、模擬BiCMOS集成電路設計核心流程

基于專業資源的學習,最終需落實到嚴謹的設計實踐中。一個典型的模擬BiCMOS IC設計流程包括:

- 規格定義與架構設計:明確電路性能指標(增益、帶寬、噪聲、功耗等),并決定哪些功能塊用BJT實現(如輸入級、輸出驅動),哪些用CMOS實現(如偏置電路、數字控制邏輯)。

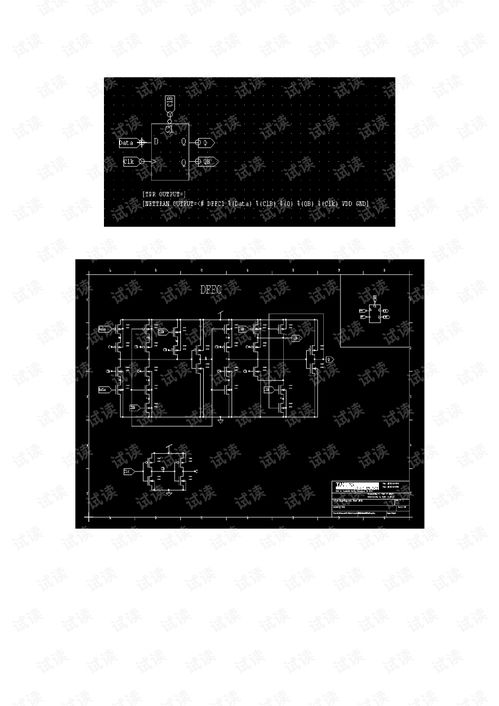

- 電路設計與仿真:在EDA環境中搭建電路原理圖。關鍵步驟包括:

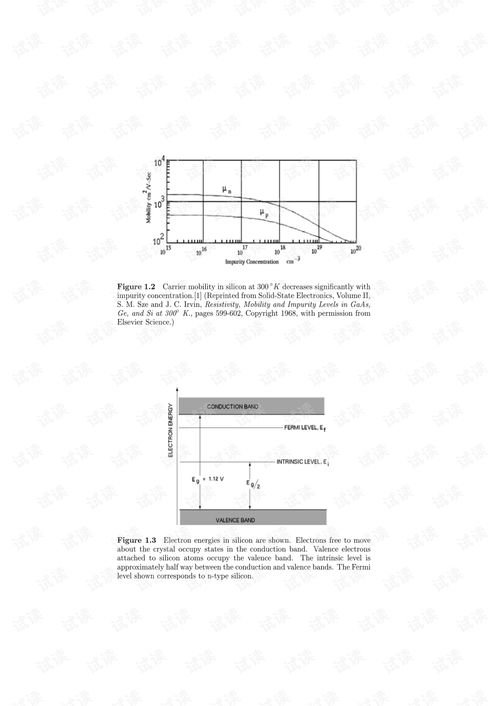

- 器件模型與選擇:深刻理解PDK中提供的BJT(NPN/PNP)和CMOS(NMOS/PMOS)的SPICE模型參數,根據速度、增益、噪聲等要求選擇合適的器件尺寸和類型。

- 直流偏置設計:確保所有晶體管工作在合適的靜態工作點,這是電路正常工作的基礎。

- 交流與小信號分析:進行AC、噪聲、瞬態仿真,優化增益、相位裕度、建立時間等動態性能。BiCMOS設計中需特別注意頻率響應和穩定性的協同優化。

- 蒙特卡洛與角落仿真:分析工藝偏差、溫度變化對電路性能的影響,確保設計的魯棒性。

- 版圖設計與驗證:這是將電路圖轉化為物理掩模版的過程,在BiCMOS設計中尤為關鍵:

- 匹配與隔離:對精度要求高的器件(如差分對)采用共質心等匹配布局;利用深N阱、隔離環等技術有效隔離BJT與CMOS器件,防止閂鎖效應和串擾。

- 寄生參數控制:精心規劃走線,最小化互連電阻、電容,特別是高頻路徑上的寄生效應。

- 設計規則檢查與版圖比對:嚴格通過DRC確保符合工藝要求,并通過LVS確保版圖與原理圖一致。

- 后仿真與流片準備:提取版圖寄生參數后進行后仿真,驗證性能是否仍滿足規格。最終生成GDSII文件交付晶圓廠流片。

四、學習建議與資源整合

對于初學者,建議遵循“理論-工具-實踐”的路徑:先通過經典教材(如Gray & Meyer的《模擬集成電路的分析與設計》)夯實器件和電路基礎;再利用CSDN等平臺的實操性資源熟悉EDA工具;最后通過一個完整的BiCMOS小項目(如一個兩級運算放大器)將知識融會貫通。積極參與相關論壇的討論,向經驗豐富的同行請教,是解決實際設計中棘手問題的有效途徑。

模擬BiCMOS設計是一門深度融合理論與工藝實踐的學科。CSDN等社區提供的豐富資源是寶貴的學習起點和問題解決參考庫,但最終的設計能力離不開對基本原理的深刻理解、嚴謹的工程實踐以及對最新工藝技術的持續跟蹤。通過系統性地學習與反復迭代設計,工程師能夠駕馭這項技術,創造出滿足高性能需求的復雜集成電路。